II. Fondements▲

II-A. Architecture▲

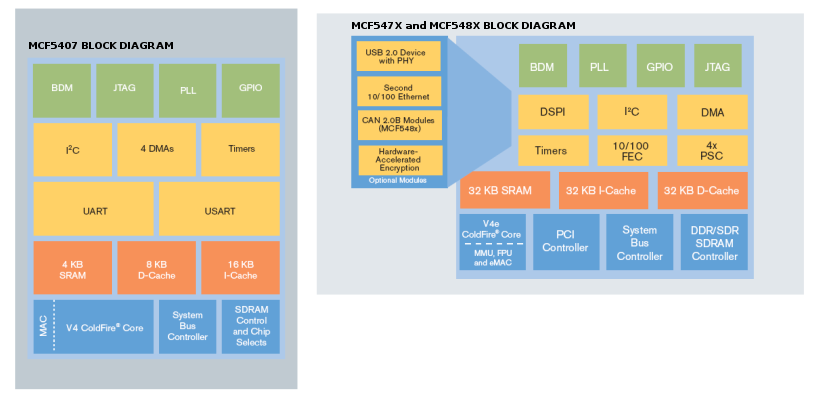

Un microcontrôleur n'est pas simplement un microprocesseur mais un ordinateur complet. Cela signifie qu'il embarque de la mémoire, des coprocesseurs (MMU, FPU, MAC...), des unités périphériques (coupleur parallèle, timers, port série ...).

Les ColdFire sont des microcontrôleurs RISC 32 bits, big-endian. Typiquement, on les trouvera dans des imprimantes réseau, des modems routeurs, des appareils d'acquisition numérique et toutes sorte d'ordinateurs embarqués.

La famille est vaste. Par exemple, le 5407 est profilé pour des applications industrielles de base (bus I2C, port parallèle, port série) alors que le 5485 doté d'une MMU et d'une FPU, possède des interfaces de plus haut niveau (PCI, USB, Ethernet, bus CAN). Ils supportent des cadences jusqu'à 200Mhz ainsi que des environnements hostiles (-45 C à +85 C). Leur coût est globalement modique. Compter de 5$ à 25$ suivant les modèles (prix constructeur).

Copyright material owned by Freescale Semiconductor, Inc. used with permission, 2005.

Les ColdFire sont donc de petites machines très performantes et peu chères destinées aux applications industrielles.

RISC ou CISC :

A proprement parler, les ColdFire ne sont pas des RISC. En effet, beaucoup

d'instructions s'exécutent en plus d'un cycle. Ce qui est contraire à la philosophie du RISC.

Pourtant on conviendra que ce n'est pas non plus un CISC. Le jeu d'instruction est réduit.

Pour celà, et pour mettre en avant la souplesse du modèle de programmation, Motorola a inventé la notion de

Variable-Length ou VL-RISC. Sans entrer plus en avant dans le débat, nous parlerons ici de RISC en convenant que

les ColdFire ne sont pas des PowerPC.

Le noeud de ces caractéristiques est avant tout l'architecture RISC. Le jeu d'instruction se limite à des commandes simples et presque toutes câblées (on parle d'instructions câblées par opposition aux instructions micro-codées). Une instruction câblée s'exécute en quelques cycles (voire un seul) alors qu'une instruction micro-codée utilise un algorithme plus complexe et demande en général quelques dizaines de cycles. Par exemple sur le 5307, les divisions prennent au moins 35 cycles là ou un décalage n'en prendra qu'un.

L'utilisation d'instructions micro-codées est lourde de conséquences et doit toujours être évaluée avec soin.

La capacité des MCF à supporter sans perte de performances des opérandes en 8, 16 ou 32 bits apporte beaucoup de souplesse. Ceci dit, en ce qui concerne l'adressage mémoire, on observe une chute des performances si les données ne sont pas alignées. Par exemple pour stocker le résultat d'une addition sur 64 bits (résultat sur 65 bits), il vaut mieux utiliser 3x32 bits ou 12x8 bits que 2x32 bits et un octet (cela est néanmoins possible). A moins d'être fortement contraint par la mémoire, la meilleure stratégie consiste à choisir une taille d'opérande et à s'y tenir. De plus, lors des départs en exception, le MCF aligne la pile sur un multiple de quatre. On peut donc dans une moindre mesure gagner un peu de ce côté la.

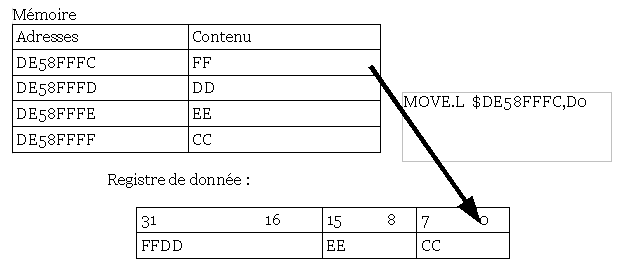

Comme nous l'avons dit le ColdFire est big-endian. Cela signifie que l'octet de poids fort est toujours du coté de l'adresse faible.

La présence d'un module de débugage permet lors de

la mise au point des programmes de suivre très simplement ce qui se passe à l'intérieur

du processeur.

Enfin signalons, qu'outre les protections de la mémoire que nous n'aborderons pas ici,

le ColdFire possède un mode utilisateur simple et un mode superviseur. Cela permet de

réduire très simplement les privilèges d'un programme.

Puisque nous avons fait le tour des généralités concernant les ColdFire nous pouvons

commencer à nous aventurer à l'intérieur...

A retenir :

Un ColdFire est un microcontrôleur, c'est-à-dire un ordinateur complet basé sur un

processeur d'architecture VL-RISC. Cela signifie qu'on peut utiliser des opérandes sur 8,

16 ou 32 bits en faisant toutefois attention à l'alignement des données en mémoire.

Par ailleurs les rares instructions micro codées (division) sont bien

plus lentes que les autres instructions. Leur usage doit donc être jaugé avec soin.

Enfin on ne le répétera jamais assez aux "Intelistes" :

L'octet de poids fort est du côté de l'adresse faible.

II-B. Registres▲

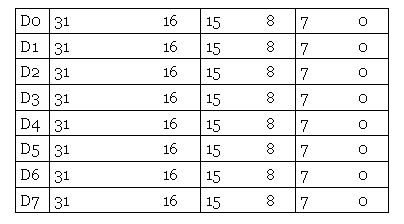

II-B-1. Les registres de donnée▲

Ils sont au nombre de huit. Généralistes, ils ont un comportement strictement équivalent :

Tous ces registres font 32 bits. Les registres de donnée peuvent être utilisées en mode 8bit (.B), 16bit (.W) ou 32bit (.L) :

- MOVE.L D0,D1 déplacera les 32 bits de D0 dans D1

- MOVE.W D0,D1 déplacera les 16 bits de poids faible de D0 dans D1

- MOVE.B D0,D1 déplacera les 8 bits de poids faible de D0 dans D1

Leur utilisation est clairement indifférenciée. Aucun n'a de propriété particulière.

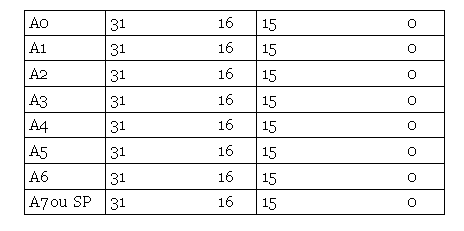

II-B-2. Les registres d'Adresse▲

Egalement au nombre de huit :

Utilisables en mode 16 (.W) ou 32 (.L) bits, seul A7 a un rôle particulier puisque c'est le pointeur de pile système (aussi appelé SP). Il ne doit donc être utilisé qu'en connaissance de cause. A6 n'est généralement utilisé que pour la gestion des variables mais il n'y a rien d'obligatoire à cela.

Même si cela est fortement déconseillé pour des raisons de performance

et de lisibilité, on peut très bien utiliser un registre d'Adresse pour

stocker des données ou inversement.

Le modèle de programmation des MCF est très souple.

Ceci dit, un fonctionnement optimal requiert l'observation

de règles de bon sens : Les adresses avec les adresses.

Les données avec les données.

II-B-3. Les registres de contrôle▲

Pour finir le tour des registres nous verrons les trois registres de contrôles les plus basiques :

- Le program counter (PC)

- Le status register (SR) ou registre d'état

- Le vector base register (VBR)

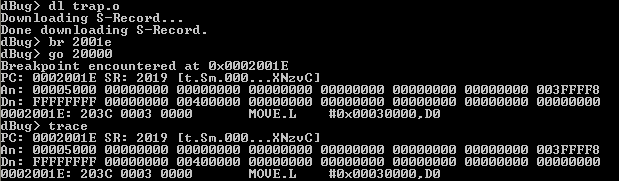

Commençons par le Program counter (PC).

C'est un registre de 32 bits qui contient l'adresse du premier mot de

l'instruction suivante. Il s'incrémente automatiquement.

C'est sur lui qu'agiront les instructions de branchement.

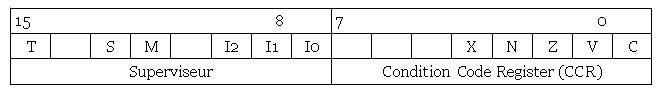

Chacun des 16 bits du registre d'état (Status register) a une fonction particulière. Les valeurs sont modifiées automatiquement par certaines instructions. La partie basse, le Condition Code Register (CCR) permet à l'utilisateur d'effectuer des tests, de récupérer une retenue ... La partie haute est réservée au superviseur.

Partie superviseur :

- T : 1 mode Trace (pour l'exécution pas à pas), 0 mode normal

- S : 1 mode Superviseur (par défaut), 0 mode Utilisateur

- M : mis à 0 par un départ en interruption

- I : masque d'interruption

Partie utilisateur :

- C et X sont des retenues. Contrairement à C, X n'est pas affecté par les comparaisons

- N négatif : positionné comme le poids fort du résultat

- Z indicateur de Zéro (Attention : vaut 1 si résultat vaut 0)

- V débordement

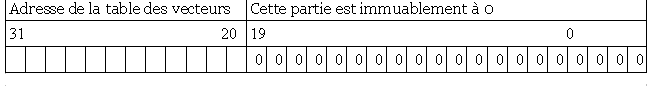

Le troisième registre auquel nous nous intéressons est le VBR (32 bits) qui contient l'adresse de base de la table des vecteurs. Lors d'un Reset le VBR est Forcé à 0. Les 20 bits de poids faible valent 0 afin que la table des vecteurs soit toujours alignée sur une adresse 0-modulo-1.

Lors d'une erreur ou lorsqu'un périphérique signale un événement, il se produit une exception. Chaque exception (erreur ou interruption) est associée à un numéro de vecteur. Ce numéro permet de retrouver l'adresse du programme à exécuter pour traiter l'exception.